|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Элементы памяти на МОП- структурах

3.1. Основные варианты

Цифровые микросхемы памяти предназначены для хранения, обработки информации. Поэтому можно пожертвовать быстродействием в пользу повышения хранимой и обрабатываемой информации.

С функциональной точки зрения схемы памяти делятся на два вида:

1. Оперативно – запоминающие устройства (ОЗУ), или что то же самое, запоминающие устройства с произвольной выборкой (ЗУПВ).

2. Постоянные запоминающие устройства (ПЗУ).

Схемы ОЗУ - это такие схемы, в которых запись и считывание информации может производиться по мере необходимости. Они применяются только для хранения данных, являющихся непосредственно объектом обработки. Информации в ОЗУ сохраняются пока включено питающее напряжение.

ОЗУ делятся на два подвида:

1. Статические – ОЗУПВ(С) {(SRAM) random access memory} – они могут хранить информацию сколь угодно долго пока подано Uпит.

2. Динамические – ОЗУПВ(D) (DRAM) - хранят информацию ограниченное время и требуют периодического восстановления данных, но зато они обладают максимальной информационной ёмкостью, а ОЗУПВ (SRAM) – максимальным быстродействием.

ПЗУ (ROM) могут хранить информацию при отключённом питании. Пример хранения информации: различные коды, данные о параметрах процессора и т.д. {Read-only memory}.

Постоянные запоминающие устройства подразделяются на четыре подвида:

- с масочным программированием (ПЗУ);

- однократно программируемые путём пережигания плавких перемычек (ППЗУ);

- ре-программируемые (стираемые) запоминающие устройства (СППЗУ);

- электрически изменяемые запоминающие устройства (ЭСППЗУ), или (ЭИПЗУ).

3.2. Статические оперативные запоминающие устройства ОЗУПВ(С)

Большая часть БИС памяти создаётся на МОП- транзисторах. Схемы на биполярных транзисторах имеют значительно меньшую информационную ёмкость.

Основной частью ЗУ является накопитель-«матрица» запоминающих элементов памяти (элементов памяти). Каждый элемент памяти предназначен для хранения одного бита информации.

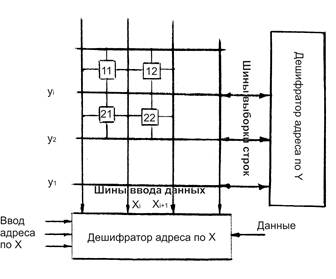

Структурная схема ОЗУПВ(С).

Каждый элемент памяти (например - 12) представляет собой ячейку матрицы, которой находится не менее четырёх транзисторов. Каждая ячейка памяти представляет собой симметричный триггер и предназначена для хранения 1 бита информации. С помощью систем шин строк «Х» и столбцов «У» возможна выборка произвольного элемента памяти.

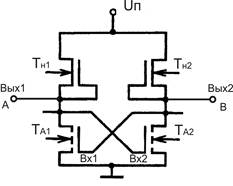

Триггер симметричный

Симметричный триггер состоит из двух инверторов (n-МОП с динамической нагрузкой) с перекрестными обратными связями (вход 1 соединен с выходом 2, а вход 2 – с выходом 1). Триггер может находится в одном из 2-х устойчивых состояний:

Симметричный триггер состоит из двух инверторов (n-МОП с динамической нагрузкой) с перекрестными обратными связями (вход 1 соединен с выходом 2, а вход 2 – с выходом 1). Триггер может находится в одном из 2-х устойчивых состояний:

- либо ТА1 – открыт, а ТА2 – закрыт;

- либо ТА2 – открыт, ТА1 – закрыт.

К точкам А и В подсоединяются управляющие транзисторы, соединенные с шинами «X» и «Y».

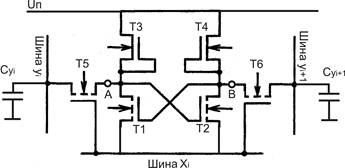

Полная схема ячейки памяти представлена на следующем рис.

- Т1 и Т2 – активные транзисторы инверторов, - Т3 и Т4 – нагрузочные транзисторы инверторов, - Т5 и Т6 – управляющие транзисторы, соединенные с шинами Yi и Yi+1.

- Т1 и Т2 – активные транзисторы инверторов, - Т3 и Т4 – нагрузочные транзисторы инверторов, - Т5 и Т6 – управляющие транзисторы, соединенные с шинами Yi и Yi+1.

При отсутствии на шине Хi напряжения выборки транзисторы Т5 и Т6 закрыты. Триггер будет «отключен» от шин столбцов Yi и Yi+1. И может сколь угодно долго хранить ранее полученную информацию, пока не отключено напряжение питания.

Запись информации.

Чтобы произвести запись информации на одну из шин «Y» столбца подают напряжение, соответствующее логическому 0, а на другую – соответствующее логической 1. Затем на шину Х подают положительный импульс выборки и управляющие транзисторы Т5 и Т6 открываются, и в плечах триггера (точках А и В) появляются соответствующие шинам Yi и Yi+1 напряжения столбцов. В результате, триггер устанавливается в одно из двух устойчивых состояний.

Считывание информации.

При считывании информации шины столбцов подключаются ко входам усилителя считывания (с большим входным сопротивлением). И при поступлении на шину «Х» положительного импульса выборки, транзисторы Т5 и Т6 открываются, и по шинам Yi и Yi+1 на входы усилителя поступают напряжения, соответствующие состоянию триггера. Эти напряжения усиливаются усилителем считывания.

В принципе, аналогичное устройство может быть построено на комплементарных структурах (что позволяет снизить потребляемую мощность и увеличить степень интеграции).

В качестве нагрузки может быть использован и высокоомный слой поликристаллического кремния.

Поиск по сайту: